# **Boolean Methods for Multi-level Logic Synthesis**

# Giovanni De Micheli Integrated Systems Centre EPF Lausanne

This presentation can be used for non-commercial purposes as long as this note and the copyright footers are not removed

© Giovanni De Micheli – All rights reserved

# Module 1

#### Objectives

▲ What are Boolean methods

#### ▲ How to compute *don't care* conditions

- ▼ Controllability

- ▼ Observability

- Boolean transformations

Exploit Boolean properties of logic functions

- Use don 't care conditions

- More complex algorithms

- ▲ Potentially better solutions

- ▲ Harder to reverse the transformations

- Used within most synthesis tools

#### Controllability don 't care set CDC<sub>in</sub>

Input patterns never produced by the environment at the network's input

# Observability don't care set ODC<sub>out</sub>

Input patterns representing conditions when an output is not observed by the environment

- Relative to each output

- ▲ Vector notation

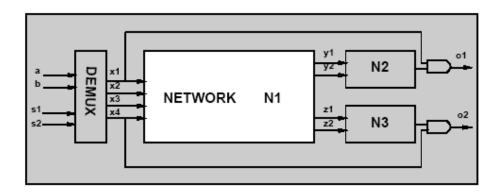

- Inputs driven by a de-multiplexer.

- $CDC_{in} = x'_1x'_2x'_3x'_4 + x_1x_2 + x_1x_3 + x_1x_4 + x_2x_3 + x_2x_4 + x_3x_4.$

• Outputs observed when

$$\begin{bmatrix} x_1 \\ x_4 \end{bmatrix} = \mathbf{1}$$

$ODC_{out} = \begin{bmatrix} x'_1 \\ x'_1 \\ x'_4 \\ x'_4 \end{bmatrix}$

Sum the controllability don't cares to each entry of the observability don't care set vector

$$\mathbf{DC}_{ext} = \mathbf{CDC}_{in} + \mathbf{ODC}_{out} = \begin{bmatrix} x_1' + x_2 + x_3 + x_4 \\ x_1' + x_2 + x_3 + x_4 \\ x_4' + x_2 + x_3 + x_1 \\ x_4' + x_2 + x_3 + x_1 \end{bmatrix}$$

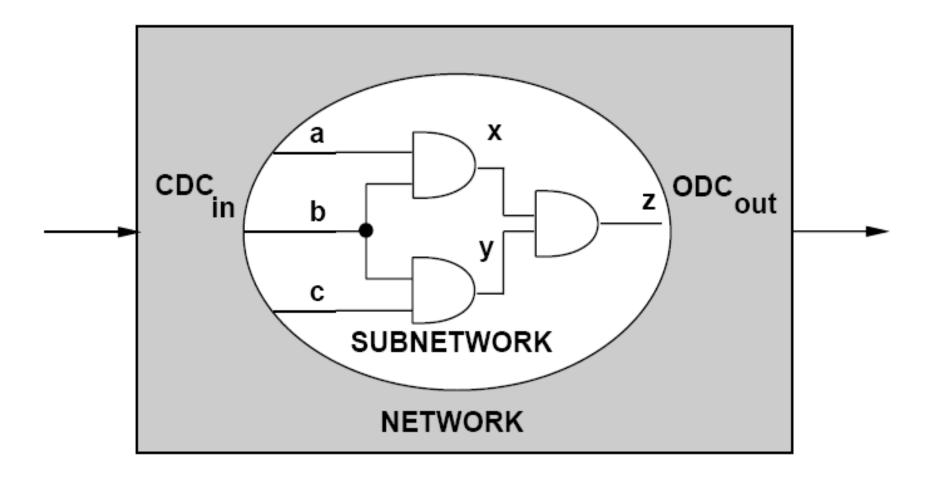

# Internal don't care conditions

- Induced by the network structure

- Controllability don 't care conditions:

- ▲ Patterns never produced at the inputs of a sub-network

- Observability don't care conditions

- ▲ Patterns such that the outputs of a sub-network are not observed

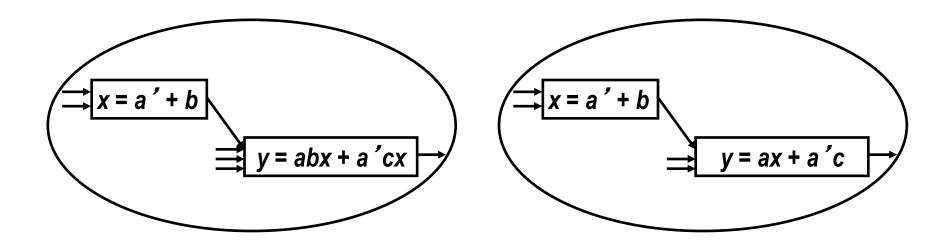

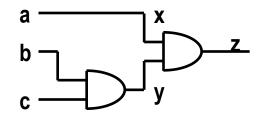

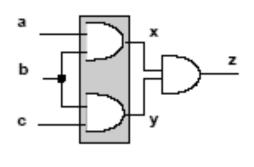

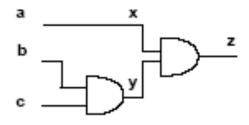

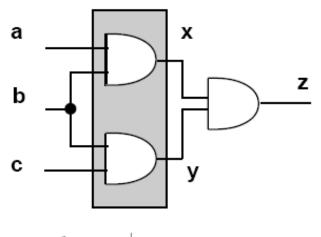

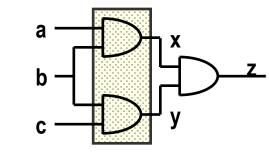

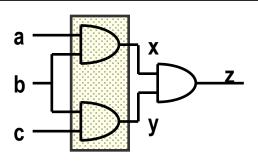

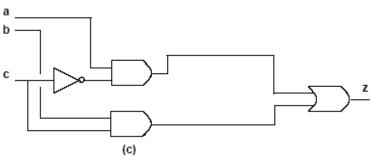

# Example of optimization with don't cares

# CDC of y includes ab' x + a' x' Minimize f<sub>y</sub> to obtain: g<sub>y</sub> = ax + a' c

Invariant of the network:

$\mathbf{x} = \mathbf{f}_{\mathbf{x}} \longrightarrow \mathbf{x} \neq \mathbf{f}_{\mathbf{x}} \subseteq \mathbf{SDC}$

• SDC =  $\sum_{\text{all internal nodes}} \mathbf{x} \oplus \mathbf{f}_{\mathbf{x}}$

# Useful to compute controllability don't cares

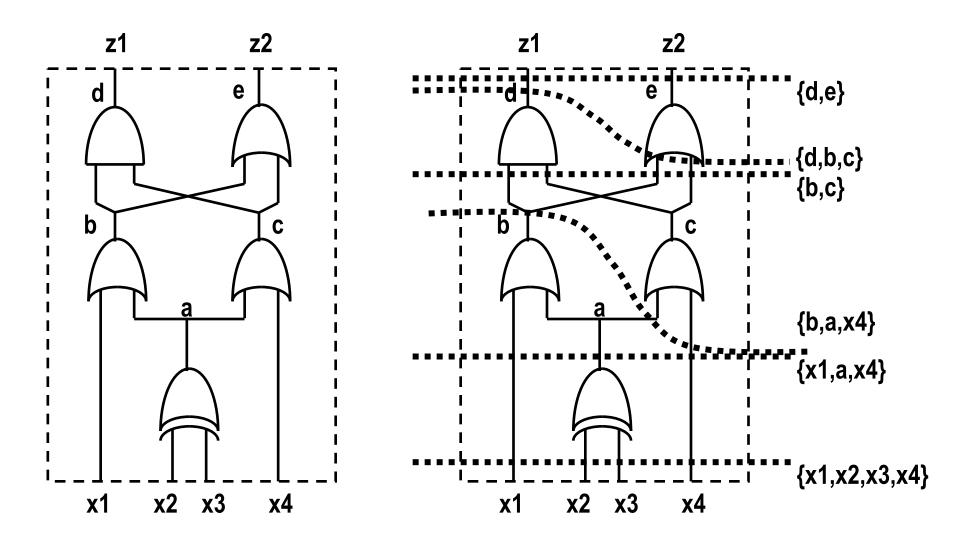

# Method 1: Network traversal algorithm

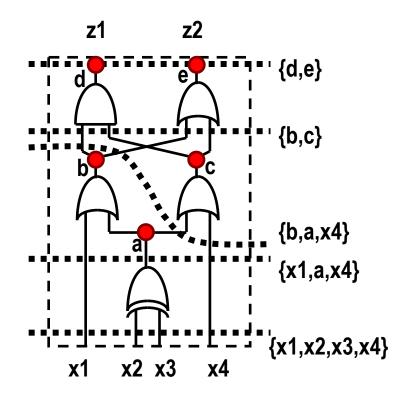

- ▲Consider initial CDC = CDC<sub>in</sub> at the primary inputs

- Consider different cutsets moving through the network from inputs to outputs

- ▲As the cutset moves forward

- Consider SDC contribution of the newly considered block

- ▼Remove unneeded variables by consensus

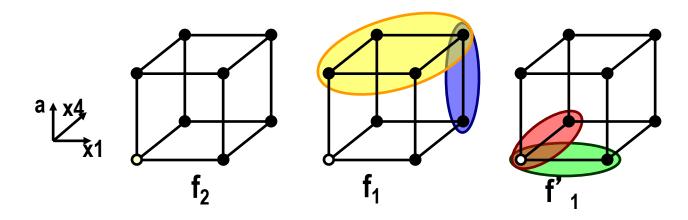

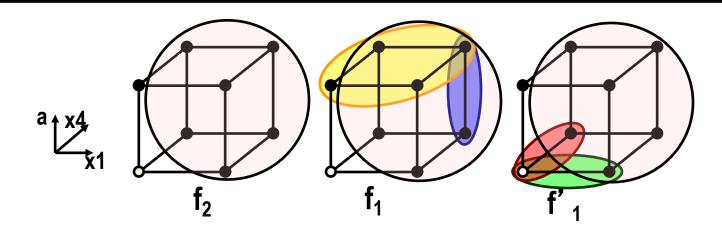

- Assume CDC<sub>in</sub> = x<sub>1</sub>' x<sub>4</sub>'

- Select vertex v<sub>a</sub>

- ▲ Contribution of  $v_a$  to CDC<sub>cut</sub>=  $a \oplus (x_2 \oplus x_3)$

- ▲ Updated CDC<sub>cut</sub>=  $x'_1 x'_4 + a \oplus (x_2 \oplus x_3)$

- ▲ Drop variables D = {x<sub>2</sub>, x<sub>3</sub>} by consensus:

- $\blacktriangle CDC_{cut} = x_1' x_4'$

- Select vertex v<sub>b</sub>

- ▲ Contribution to  $CDC_{cut}$ : b  $\oplus$  (x<sub>1</sub> + a).

- ▼ Updated CDC<sub>cut</sub> =  $x_1' x_4' + b \oplus (x_1 + a)$

- ▲ Drop variables x<sub>1</sub> by consensus:

- $\checkmark$  CDC<sub>cut</sub> = b' x<sub>4</sub>' + b' a

# **CDC** Computation

```

CONTROLLABILITY(G_n(V, E), CDC_{in}) {

```

C = V';

**};**

$CDC_{cut} = CDC_{in};$

foreach vertex  $v_x \in V$  in topological order {

$C = C U v_x;$  $CDC_{cut} = CDC_{cut} + f_x \oplus x;$  $D = \{v \in C \text{ s.t. all direct successors of } v \text{ are in } C\}$ foreach vertex  $v_v \in D$  $CDC_{cut} = C_v(CDC_{cut});$ C = C - D; $CDC_{out} = CDC_{cut};$

- Method 2: range or image computation

- Consider the function f expressing the behavior of the cutset variables in terms of primary inputs

- CDC<sub>cut</sub> is the complement of the range of f when CDC<sub>in</sub> = 0

- CDC<sub>cut</sub> is the complement of the image of (CDC<sub>in</sub>)' under f

- The range and image can be computed recursively

- ▲ Terminal case: scalar function

- ▲ The range of y = f(x) is y + y' (any value) unless f (or f') is a tautology and the range is y (or y')

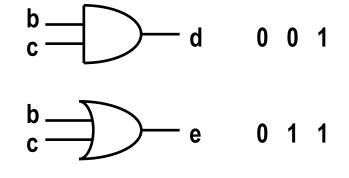

$\bullet range(f) = d range((b+c)|_{d=bc=1}) + d' range((b+c)|_{d=bc=0})$

- When d = 1, then bc =  $1 \rightarrow b + c = 1$  is TAUTOLOGY

- If I choose 1 as top entry in output vector:

- ▲ the bottom entry is also 1.

$$\left[\begin{array}{c}1\\?\end{array}\right]\rightarrow\left[\begin{array}{c}1\\1\end{array}\right]$$

• When d = 0, then bc =  $0 \rightarrow b+c = \{0,1\}$

♦ If I choose 0 as top entry in output vector:

▲ The bottom entry can be either 0 or 1.

◆ range(f) = de + d' (e + e') = de + d' = d' + e

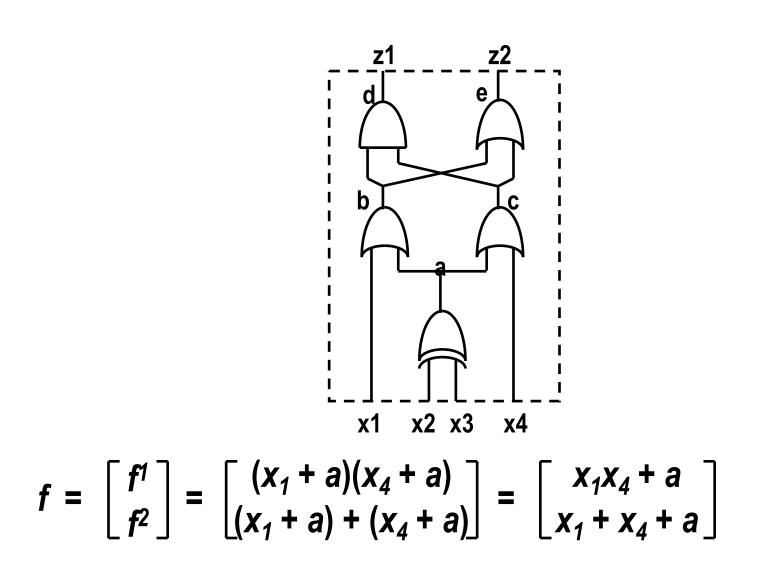

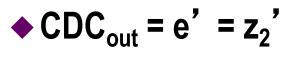

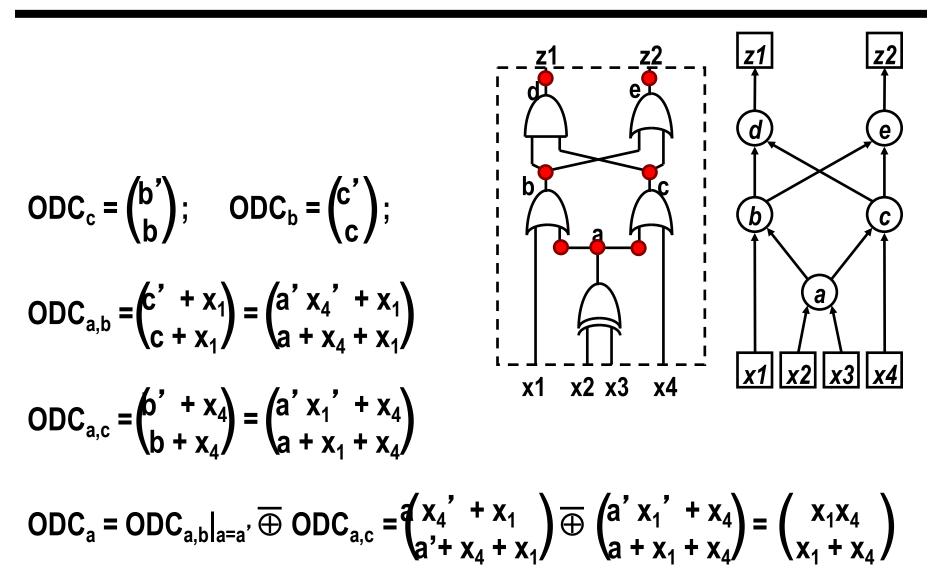

$range(f) = d \ range(f^{2}|_{(x_{1}x_{4} + a)=1}) + d' \ range(f^{2}|_{(x_{1}x_{4} + a)=0})$ = d \ range(x\_{1} + x\_{4} + a|\_{(x\_{1}x\_{4} + a)=1}) + d' \ range(x\_{1} + x\_{4} + a|\_{(x\_{1}x\_{4} + a)=0}) = d \ range(1) + d' \ range(a' (x\_{1} \oplus x\_{4})) = de + d' (e + e') = e + d'  $\bullet CDC_{out} = (e + d')' = de' = z_{1}z_{2}'$

(c) Giovanni De Micheli

$$CDC_{in} = x'_{1} x'_{4}$$

$$\int_{a} \int_{a} \int$$

$image(f) = d image(f^2|_{(x_1x_4 + a)=1}) + d' image(f^2|_{(x_1x_4 + a)=0})$

= d image( $x_1 + x_4 + a|_{(x_1x_4 + a)=1}$ ) + d' image( $x_1 + x_4 + a|_{(x_1x_4 + a)=0}$ ) = d image(1) + d' image(1) = de + d' e

= e

(c) Giovanni De Micheli

#### Complementary to controllability

- ▲ Analyze network from outputs to inputs

- More complex because network has several outputs and observability depends on output

- Observability may be understood in terms of perturbations

- ▲ If you flip the polarity of a signal at net *x*, and there is no change in the outputs, then **x** is not observable

# **Observability** *don* 't care conditions

- Conditions under which a change in polarity of a signal x is not perceived at the output

- ♦ If there is an explicit representation of the function, the ODC is the complement of the Boolean difference

ODC = (∂f / ∂x)'

- Often, the terminal behavior is described implicitly

Applying chain rule to Boolean difference is computationally hard

#### Consider network from outputs to input

- At root

- ▲ ODC<sub>out</sub> is given

- ▲ It may be empty

# At internal nodes:

- ▲ Local function  $y = f_y(x)$

- $\triangle ODC_{x} = (\partial f_{y} / \partial x)' + ODC_{y}$

Observability don't care set has two components:

# Observability of the local function and observability of the network beyond the local block

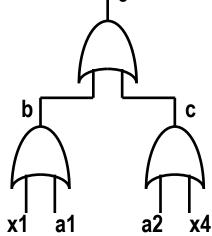

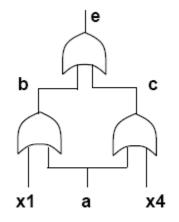

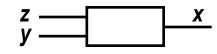

e e = b + c $b = x_1 + a_1$ b  $c = x_4 + a_2$

♦ Assume ODC<sub>out</sub> = ODC<sub>e</sub> = 0

- $ODC_{b} = (\partial f_{e}/\partial b)' = (b + c)|_{b=1} \oplus (b + c)|_{b=0} = c$

- $\bullet$  ODC<sub>c</sub> = ( $\partial f_e / \partial c$ )' = b

$ODC_{x_1} = ODC_{b} + (\partial f_{b} / \partial x_{1})' = c + a_1$

General networks have forks and fanout reconvergence

For each fork point, the contribution to theODC depends on both paths

Network traversal cannot be applied in a straightforward way

More elaborate analysis is needed

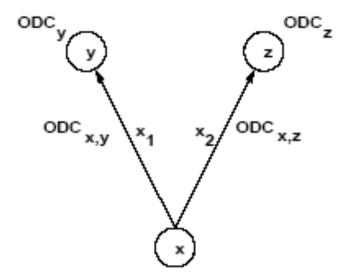

# **Two-way fork**

Compute ODC sets associated with edges

- Recombine ODCs at fork point

- Theorem:

- $ODC_{x} = ODC_{x,y|x=x'} \bigoplus ODC_{x,z}$

- ▲ ODC<sub>x</sub> = ODC<sub>x,z|x=x'</sub>  $\bigoplus$  ODC<sub>x,y</sub>

# Multi-way forks can be reduced to a sequence of two-way forks

- Controllability don 't cares are derived by image computation

- ▲ Recursive algorithms and data structure are applied

- Observability don't cares are derived by backward traversal

- Exact and approximate computation

- ▲ Approximate methods compute *don 't care* subsets

# Transformations with don't cares

#### Boolean simplification

- ▲ Generate local DC set for local functions

- ▲ Use heuristic minimizer (e.g., Espresso)

- Minimize the number of literals

#### Boolean substitution:

- ▲ Simplify a function by adding one (ore more) inputs

- ▲ Equivalent to simplification with global *don't care* sets

Substitute q = a + cd into f<sub>h</sub> = a + bcd + e

▲ Obtain  $f_h = a + bq + e$

Method

▲ Compute SDC including q ⊕ (a+cd) = q' a +q' cd + qa' (cd)'

▲ Simplify  $f_h = a + bcd + e$  with DC = q' a + q' cd + qa' (cd)'

▲ Obtain f<sub>h</sub> = a + bq +e

Result

▲ Simplified function has one fewer literal by changing the support of f<sub>h</sub>

# **Simplification operator**

#### Cycle over the network blocks

▲ Compute local don't care conditions

▲ Minimize

Issues:

▲ Don't care sets change as blocks are being simplified

- ▲ Iteration may not have a fixed point

- ▲ It would be efficient to parallelize some simplifications

- Minimizing a function at a block x is the replacement of a local function f<sub>x</sub> with a new function g<sub>x</sub>

- This is equivalent to perturbing the network locally by

$\bullet \ \mathbf{\delta}_{x} = \mathbf{f}_{x} \oplus \mathbf{g}_{x}$

- Conditions for a feasible replacement

- ▲ Perturbation bounded by local don't care sets

- ▲  $\delta_x$  included in DC<sub>ext</sub> + ODC + CDC

# Smaller, approximate don 't care sets can be used

▲ But have smaller degrees of freedom

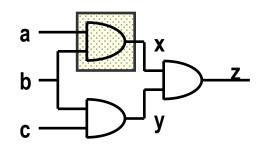

◆ No external *don 't care* set.

• Replace AND by wire:  $g_x = a$

Analysis:

▲ δ = f<sub>x</sub> ⊕ g<sub>x</sub> = ab ⊕ a = ab' ▲ ODC<sub>x</sub> = y' = b' + c' ▲ δ = ab' ⊆ DC<sub>x</sub> = b' + c' ⇒ feasible!  Parallel minimization of logic blocks is always possible when blocks are logically independent

Partitioned network

Within a connected network, logic blocks affect each other

Doing parallel minimization is like introducing multiple perturbations

▲ But it is attractive for efficiency reasons

Perturbation analysis shows that degrees of freedom cannot be represented by just an upper bound on the perturbation

Boolean relation model

Perturbations at x and y are related because of the reconvergent fanout at z

Cannot change simultaneously

▲ ab into a

▲ cb into c

#### **Boolean relation model**

| a | b | c | x,y                |

|---|---|---|--------------------|

| 0 | 0 | 0 | $\{ 00, 01, 10 \}$ |

| 0 | 0 | 1 | $\{ 00, 01, 10 \}$ |

| 0 | 1 | 0 | { 00, 01, 10 }     |

| 0 | 1 | 1 | $\{00, 01, 10\}$   |

| 1 | 0 | 0 | { 00, 01, 10 }     |

| 1 | 0 | 1 | { 00, 01, 10 }     |

| 1 | 1 | 0 | $\{00, 01, 10\}$   |

| 1 | 1 | 1 | { 11 }             |

| a | b | c | x,y |

|---|---|---|-----|

| 1 | * | * | 10  |

| * | 1 | 1 | 01  |

Boolean relation minimization is the correct approach to handle Boolean optimization at multiple vertices

#### Necessary steps

- ▲ Derive equivalence classes for Boolean relation

- ▲ Use relation minimizer

- Practical considerations

- ▲ High computational requirement to use Boolean relations

- ▲ Use approximations instead

- Determine a subset of *don't care* sets which is safe to use in a parallel minimization

- ▲ Remove those degrees of freedom that can lead to transformations incompatible with others effected in parallel

- Using compatible don 't care sets, only upper bounds on the perturbation need to be satisfied

- Faster and efficient method

### Parallel optimization at two vertices

- First vertex x

- ▲ CODC equal to ODC set

- $\triangle CODC_x = ODC_x$

### Second vertex y

▲ CODC is smaller than its ODC to be safe enough to allow for transformations permitted by the first ODC

$\triangle CODC_y = C_x (ODC_y) + ODC_y ODC'_x$

### Order dependence

## Example (2)

### Allowed perturbation:

#### Disallowed perturbation:

$$▲$$

f<sub>x</sub> = ab → g<sub>x</sub> = a.

$▲$  δ<sub>x</sub> = ab ⊕ a = ab'  $⊆$  CODC<sub>x</sub> = abc'

#### Boolean methods Summary

Boolean methods are powerful means to restructure networks

- ▲ Computationally intensive

- Boolean methods rely heavily on don't care computation

- ▲ Efficient methods

- ▲ Possibility to subset the *don't care* sets

- Boolean method often change the network substantially, and it is hard to undo Boolean transformations

## Module 2

#### Objectives

▲ Testability

▲ Relations between testability and Boolean methods

- Generic term to mean easing the testing of a circuit

- Testability in logic synthesis context

- ▲ Assume combinational circuit

- ▲ Assume single/multiple stuck-at fault

- Testability is referred to as the possibility of generating test sets for all faults

- ▲ Property of the circuit

- ▲ Related to fault coverage

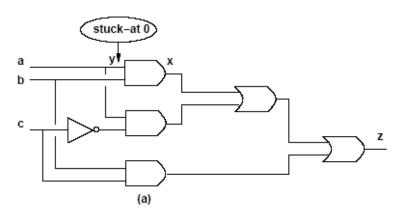

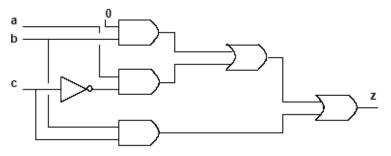

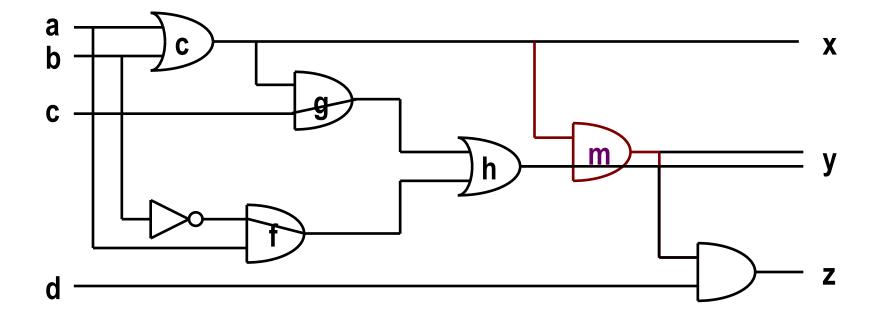

#### Net y stuck-at 0

- ▲ Input pattern that sets y to TRUE

- ▲ Observe output

- ▲ Output of faulty circuit differs from correct circuit

#### Net y stuck-at 1

- ▲ Input pattern that sets y to FALSE

- ▲ Observe output

- ▲ Output of faulty circuit differs from correct circuit

Testing is based on controllability and observability

### Stuck-at 0 on net y

A{ Input vector t such that y(t) ODC' y (t) = 1 }

## Stuck-at 1 on net y

A{ Input vector t such that y' (t) ODC' y (t) = 1 }

## Using testing methods for synthesis

### Redundancy removal

- ▲ Use ATPG to search for untestable fault

- If stuck-at 0 on net y is untestable:

- ▲ Set y = 0

- ▲ Propagate constant

- If stuck-at 1 on net y is untestable

- ▲ Set y = 1

- Propagate constant

## Iterate for each untestable fault

## **Redundancy removal and perturbation analysis**

### Stuck-at 0 on y

**A**y set to 0. Namely  $g_x = f_x|_{y=0}$

▲Perturbation:

$\mathbf{\nabla} \boldsymbol{\delta} = \mathbf{f}_{\mathbf{x}} \oplus \mathbf{f}_{\mathbf{x}}|_{\mathbf{y}=\mathbf{0}} = \mathbf{y} \cdot \partial \mathbf{f}_{\mathbf{x}} / \partial \mathbf{y}$

## ♦ Perturbation is feasible ⇔ fault is untestable

- **A**No input vector t can make  $y(t) \cdot ODC_y'(t)$  true

- ▲No input vector t can make  $y(t) \cdot ODC_x'(t) \cdot \partial f_x / \partial y$  true ▼Because ODC<sub>y</sub> = ODC<sub>x</sub> + ( $\partial f_x / \partial y$ )'

## **Redundancy removal and perturbation analysis**

## Assume untestable stuck-at 0 fault.

- $\mathbf{y} \cdot \mathbf{ODC}_{x}' \cdot \partial f_{x} / \partial y \subseteq \mathbf{SDC}$

- Local don't care set:

- $\mathbf{A}\mathbf{D}\mathbf{C}_{\mathbf{x}} \supseteq \mathbf{O}\mathbf{D}\mathbf{C}_{\mathbf{x}} + \mathbf{y} \cdot \mathbf{O}\mathbf{D}\mathbf{C}_{\mathbf{x}}' \cdot \partial \mathbf{f}_{\mathbf{x}} / \partial \mathbf{y}$

- $\blacktriangle DC_x \supseteq ODC_x + y \cdot \partial f_x / \partial y$

## • Perturbation $\delta = y \cdot \partial f_x / \partial y$

▲Included in the local don't care set

# Rewiring

#### Extension to redundancy removal

- Add connection in a circuit

- Create other redundant connections

- Remove redundant connections

#### Iterate procedure to reduce network

- ▲ A connection corresponds to a wire

- Rewiring modifies gates and wiring structure

- ▲ Wires may have specific costs due to distance

#### Synthesize fully testable circuits

- ▲ For single or multiple stuck-at faults

- Realizations

- ▲ Two-level forms

- ▲ Multi-level networks

- Since synthesis can modify the network properties, testability can be addressed during synthesis

## Full testability for single stuck-at faults:

▲ Prime and irredundant covers

## Full testability for multiple stuck-at faults

▲ Prime and irredundant cover when

- ▼ Single output function

- ▼No product-term sharing

- ▼Each component is prime and irredundant

### Example f = a'b' + b'c + ac + ab

- Consider logic networks with local functions in sop form

- Prime and irredundant network

- ▲ No literal and no implicant of any local function can be dropped

- ▲ The AND-OR implementation is fully testable for single *stuck-at* faults

- Simultaneous prime and irredundant network

- ▲ No subsets of literals and no subsets of implicants can be dropped

- ▲ The AND-OR implementation is fully testable for multiple *stuck-at*s

- Heuristic logic minimization (e.g., Espresso) is sufficient to insure testability of two-level forms

- To achieve fully testable networks, simplification has to be applied to all logic blocks with full *don't care* sets

- In practice, don't care sets change as neighboring blocks are optimized

- Redundancy removal is a practical way of achieving testability properties

## **Summary – Synthesis for testability**

- There is synergy between synthesis and testing

Don't care conditions play a major role in both fields

- Testable network correlate to a small area implementation

- Testable network do not require to slow-down the circuit

- Algebraic transformations preserve multi-fault testability, and are preferable under this aspect