# **Timing Issues in Multi-level Logic Optimization**

# Giovanni De Micheli Integrated Systems Centre EPF Lausanne

This presentation can be used for non-commercial purposes as long as this note and the copyright footers are not removed

© Giovanni De Micheli – All rights reserved

# Module 1

#### Objectives:

- ▲ Timing verification:

- ▲ Delay modeling

- ▲ Critical paths

- ▲ The false path problem

# **Timing verification and optimization**

## Verification:

#### ▲ Check that a circuit runs at speed

- ▼ Satisfies I/O delay constraints

- ▼ Satisfies cycle-time constraints

## Optimization:

#### ▲ Minimum *delay*

▼ ( subject to area constraints )

#### ▲ Minimum *area*

▼ Subject to *delay* constraints

# **Delay modeling**

#### Gate delay modeling:

#### Straightforward for bound networks

- ▼ Cell library models: d = a + b Cap

- Cap due to fanout and wiring

- ▲ Approximations for unbound networks

- ▼ Virtual gates

#### Network delay modeling:

- ▲ Compute signal propagation

- Topological methods

- Logic/topological methods (false paths)

# **Network delay modeling**

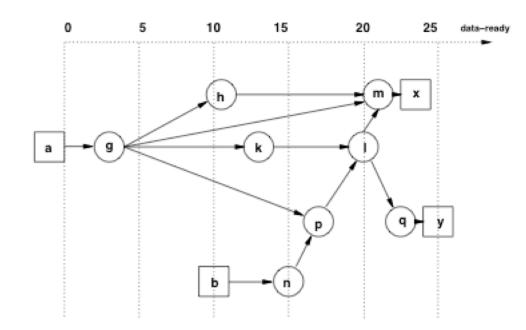

- For each vertex v<sub>i</sub>

- Propagation delay d<sub>i</sub>:

▲ I/O propagation delays are usually zero

#### Data-ready time t<sub>i</sub>:

▲ Input data-ready time denote when inputs are available

▲ Computed elsewhere by forward traversal

$t_i = d_i + \max_j t_j \quad s.t. (v_j, v_i) \in E$

Propagation delays:

▲

$$d_g = 3$$

;  $d_h = 8$ ;  $d_m = 1$ ;  $d_k = 10$ ;  $d_l = 3$

▲  $d_n = 5$ ;  $d_p = 2$ ;  $d_p = 2$ ;  $d_x = 2$ ;  $d_y = 3$

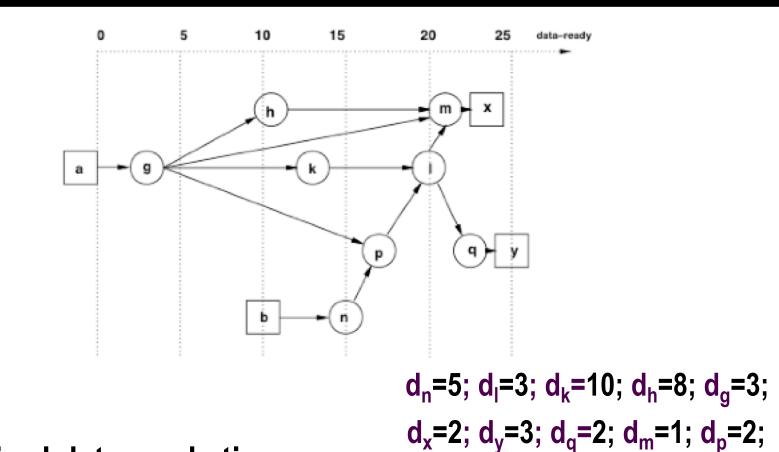

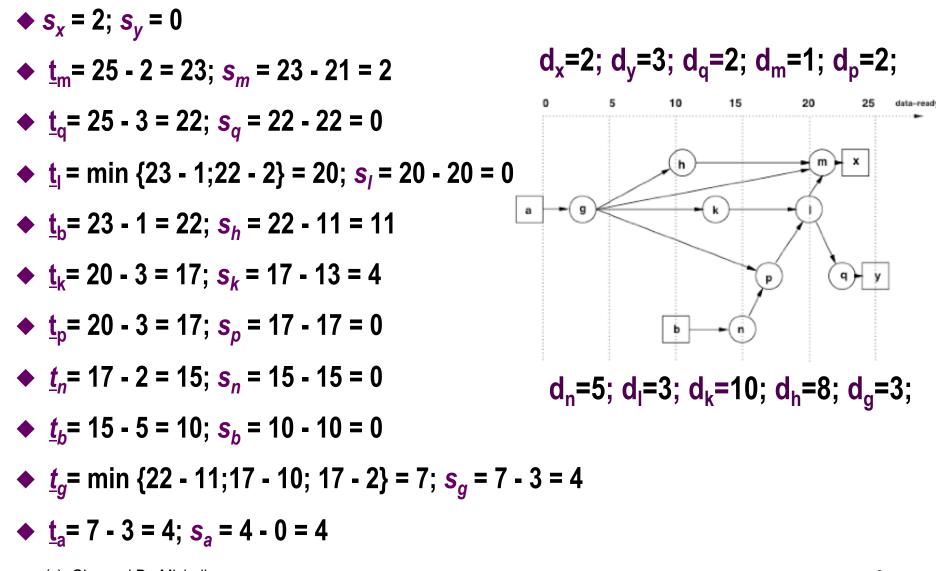

# **Network delay modeling**

#### •For each vertex $v_i$ :

#### Required data-ready time t<sub>i</sub> :

▲ Specified at the primary outputs

▲ Computed elsewhere by *backward traversal*

$\underline{t}_i = \min_j \ \underline{t}_j - d_j \ s.t. (v_i, v_j) \ \varepsilon E$

Slack s<sub>i</sub>:

# ▲ Difference between required and actual data-ready times $s_i = \underline{t}_j - t_i$

Required data-ready times:

$\blacktriangle$  <u>t</u><sub>x</sub>= 25 and <u>t</u><sub>y</sub>= 25

(c) Giovanni De Micheli

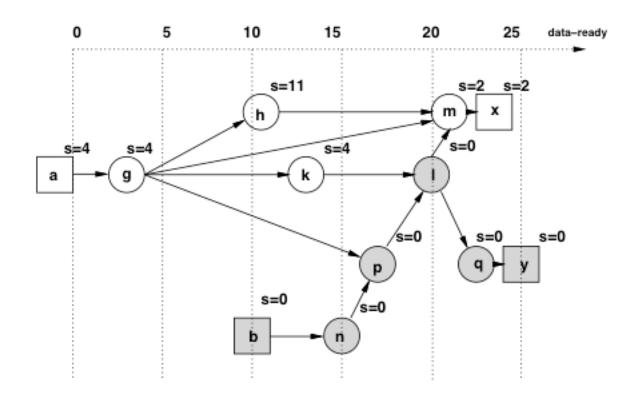

Assume topologic computation of :

- ▲ Data-ready by forward traversal

- ▲ Required data-ready by backward traversal

## Topological critical path :

- ▲ Input/output path with zero slacks

- Any increase in the vertex propagation delay affects the output data-ready time

#### A topological critical path may be false:

▲ No event can propagate along that path

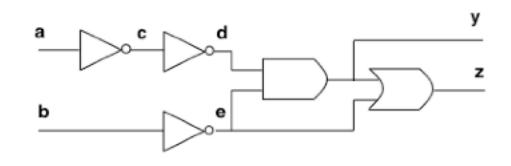

- All gates have unit delay

- All inputs ready at time 0

- Longest topological path :  $(V_a, V_c, V_d, V_y, V_z)$  :

- A Path delay: 4 units

- Critical true path:  $(V_a, V_c, V_d, V_y)$ :

- Path delay: 3 units

(c) Giovanni De Micheli

- A path in a logic network is sensitizable if an event can propagate from its tail to its head

- A critical *path* is a sensitizable path of maximum weight

- Only sensitizable paths should be considered

- Non-sensitizable paths are false and can be discarded

# **Sensitizable paths**

#### Path:

- Ordered set of vertices

- Inputs to a vertex:

- ▲ Direct predecessors

- ◆ Side-inputs of a vertex:

- ▲ Inputs not on the path

# **Sensitization condition**

◆Path:  $P = (v_{xo}, v_{x1}, ..., v_{xm})$

An event propagates along *P* if :

$$\partial f_{xi} / \partial x_{i-1} = 1$$

,  $i = 1, 2, ..., m$

Remarks :

- Boolean differences are function of the side-inputs and values on the side-inputs may change

- Boolean differences must be true at the time that the event propagates

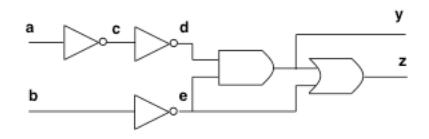

- Path:  $(V_a, V_c, V_d, V_y, V_z)$

- $\land \partial f_v / \partial d = e = 1$  at time 2

- $\land \partial f_z / \partial y = e' = 1$  at time 3

Not dynamically sensitizable because e settles at time 1

# Modes for delay computation

#### Transition mode:

#### Variables assumed to hold previous values

- ▼ Model circuit node capacitances

- ▲ *Two test vectors* are needed

## Floating mode:

- ▲ Circuit is assumed to be memoryless

- ▼ Variables have unknown value until set by input test vector

- ▲ Need only one test vector

## **Static co-sensitization**

#### Assumption:

- ▲ Circuit modeled by AND, OR, INV gates

- ▲ *INV* are irrelevant to the analysis

- ▲ Floating mode

#### Controlling values:

- ▲ 0 for AND gate

- ▲1 for *OR* gate

# Gate has controlled value when controlling value is present

# **Static co-sensitization**

- •Path:  $P = (v_{xo}, v_{x1}, ..., v_{xm})$

- A vector *statically co-sensitizes* a path to 1 (or to 0) if :

- $\mathbf{x}_m = \mathbf{1}$  (or 0) and

- ▲  $v_{xi-1}$  has a controlling value whenever  $v_{xi}$  has a controlled value

#### Necessary condition for a path to be true

Sufficient conditions are based on the timing of the signal

## False path detection test

#### For all input vectors, one of the following is true:

- ▲ (1) A gate is controlled and

- ▼ the path provides a non-controlling value

- ▼ a side-input provides a controlling value

- ▲ (2) A gate is controlled and

- ▼ The path and a side-input have controlling values

- ▼ The side-input presents the controlling value first

- ▲ (3) A gate is not controlled and

- ▼ A side-input presents the non-controlling value last

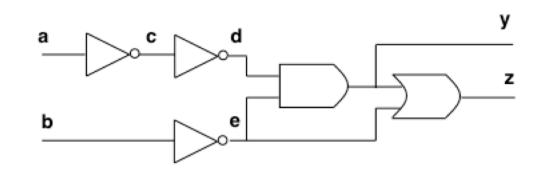

**•**Path:  $(v_a, v_c, v_d, v_y, v_z)$

◆For *a* = 0, *b* = 0 :

▲ Condition (1) occurs at the OR gate

◆ For *a* = 0, *b* = 1 :

▲ Condition (2) occurs at the AND gate

◆ For *a* = 1, *b* = 0 :

▲ Condition (2) occurs at the OR gate

◆ For *a* = 1, *b* = 1 :

- Condition (1) occurs at the AND gate

- (c) Giovanni De Micheli

Check if circuit works at speed t

▲ Verify that all true paths are faster than <u>t</u>

▲ Show that all paths slower than <u>t</u> are false

- Compute groups of false paths

- Compute critical true path:

- **\blacktriangle** Binary search for values of **<u>t</u>**

- ▲ Show that all paths slower that <u>t</u> are false