Hello everyone,

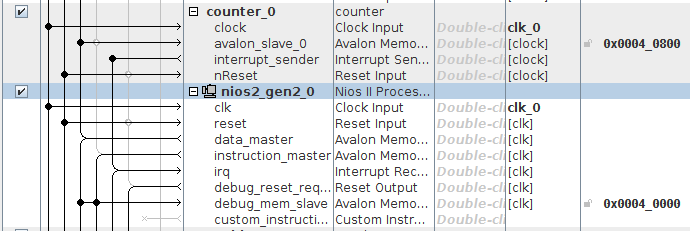

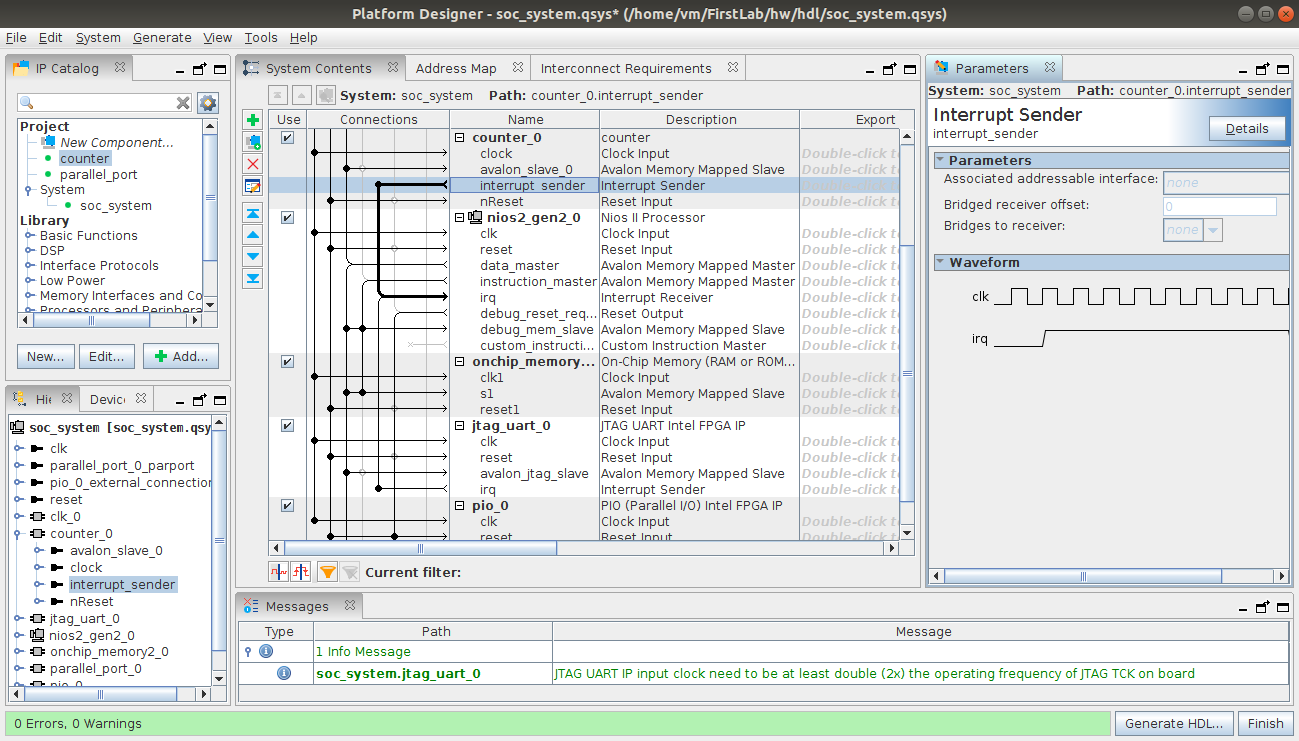

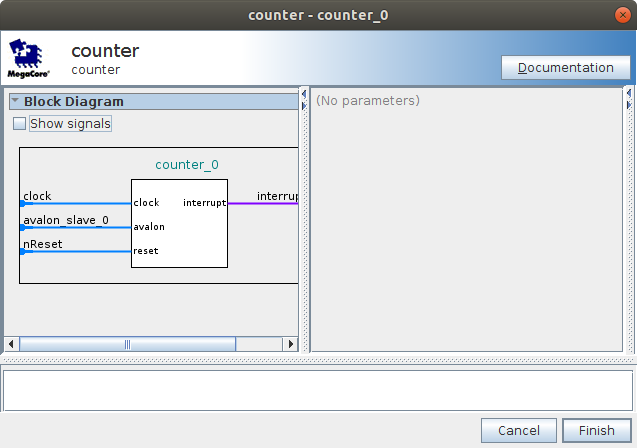

How do we make an interrupt work (the function alt_ic_isr_register as described in 'Interrupt times measurement by softwareFile')? The counter decrements from a set value to 0, where the interrupt should occur. However, the counter goes on (underflow) and the my_isr function is never properly executed. As far as we understand it, the IRQ output (last line in the VHDL file) should correctly be set to '1', since we checked all the conditions in the corresponding if clause (c main function).

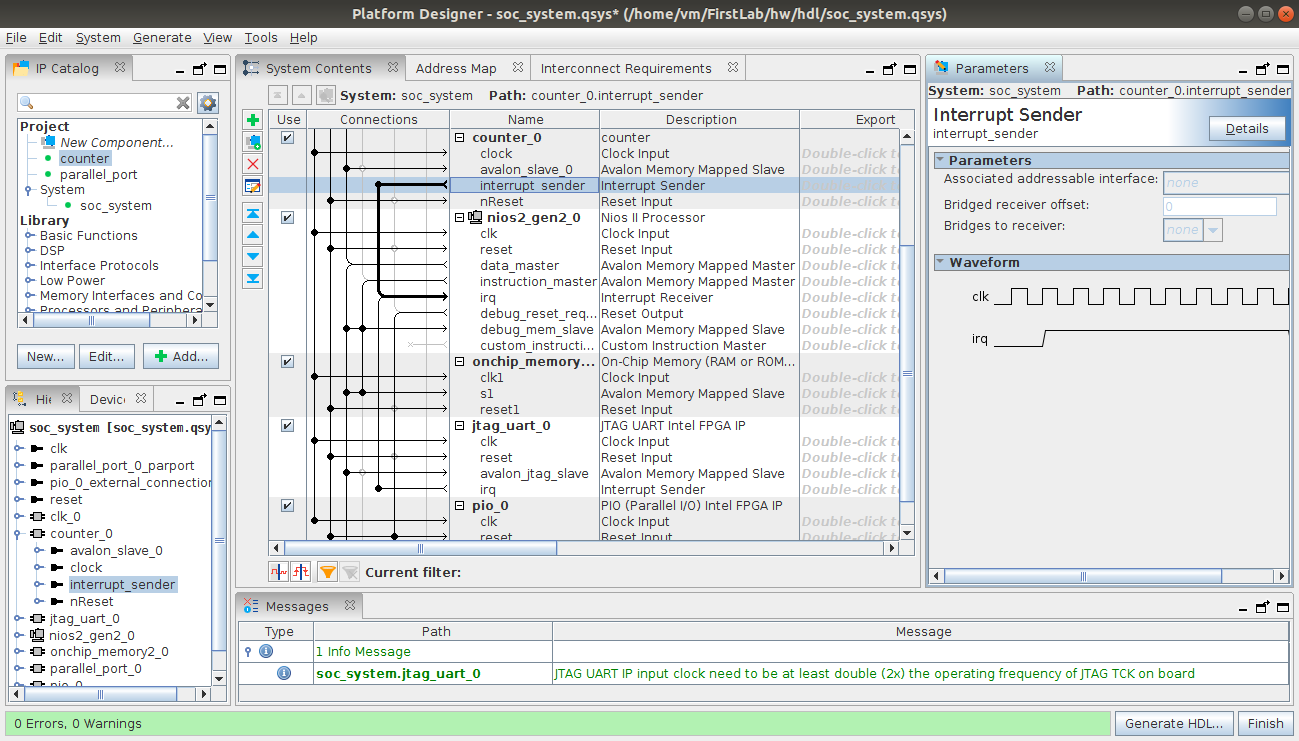

Please the VHDL (for the counter) and c codes in the following links: