Hello,

I have a question regarding Lab 3. The focus is on serial communication between the PC and the two Nios-II processors.

I read in details the Multiprocessor design example from Intel/Altera at the link given on the Moodle page (Intel Link to tutorial). I noticed that they have multiple JTAG UART instanced on the same USB cable (they have 6 instances running on Fig 1-11 p.35/44 in the tutorial) and they can all output data at the same time.

In the Lab 3 instructions, we are asked to use a JTAG UART (cpu_0) and an UART component cpu_1). However, I didn't find to which pins to connect the two serial wires UART_TX and UART_RX in the FPGA part (there are two UART pins in the De1_SoC_top_level.vhd but they are connected to the HPS side of the board).

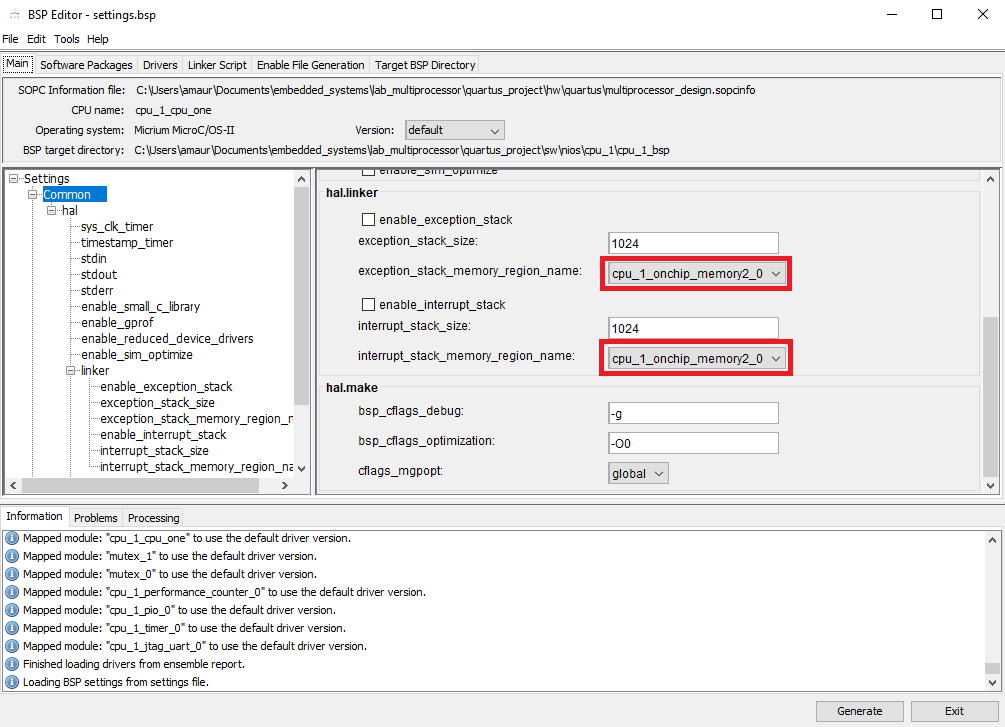

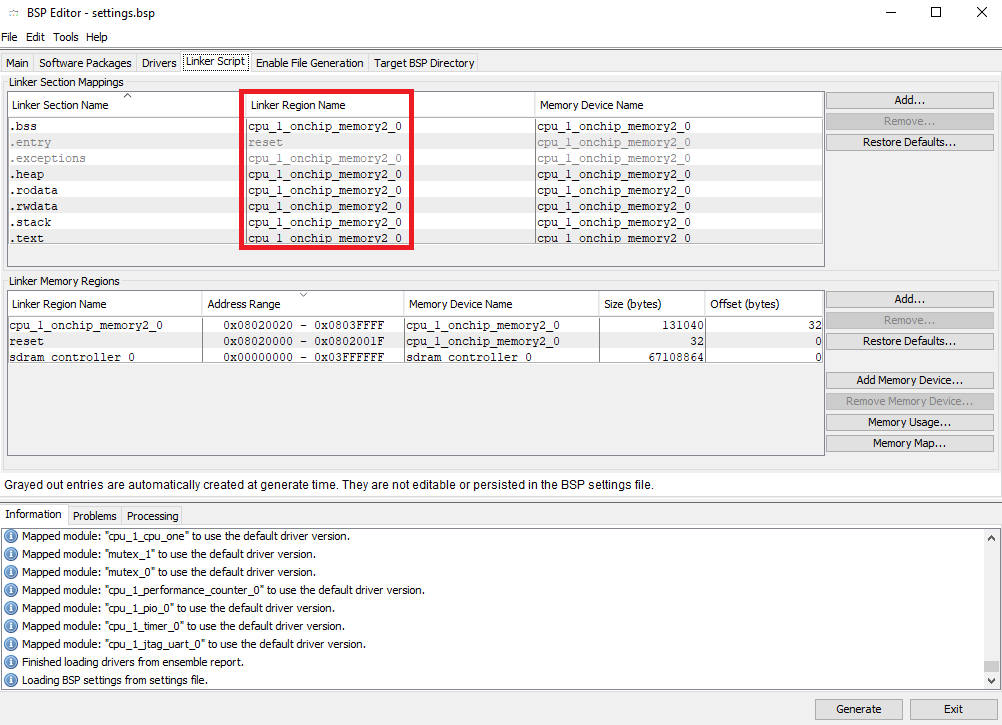

To fix this, I tried using two JTAG UART (one per cpu). Using the Nios-II terminal, I can see both JTAG UART interfaces and connect to both of them at the same time (cf. figure below). When I start the processors one by one, I can see the outputs of the first processor in one terminal, but as soon as I start the second, the first terminal stops updating and I don't receive any more outputs.

Does anyone know how to fix this? If not, how can I connect the UART module to one of the USB ports on the board?

Thanks a lot.

Amaury