I have a problem with memory write accesses with a custom Avalon Master using the SDRAM controller on the De1-SoC board.

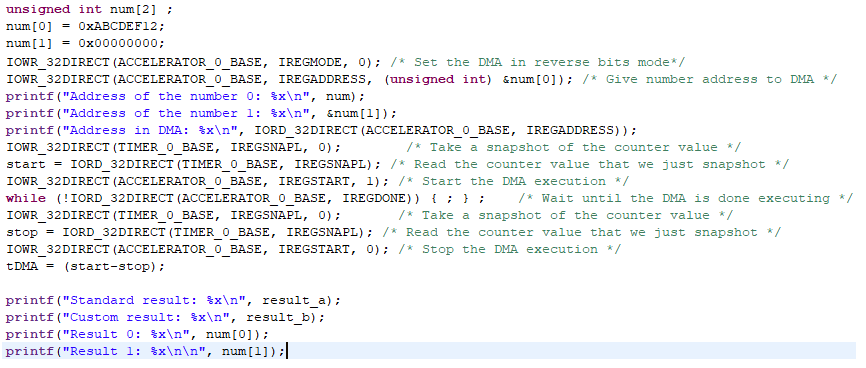

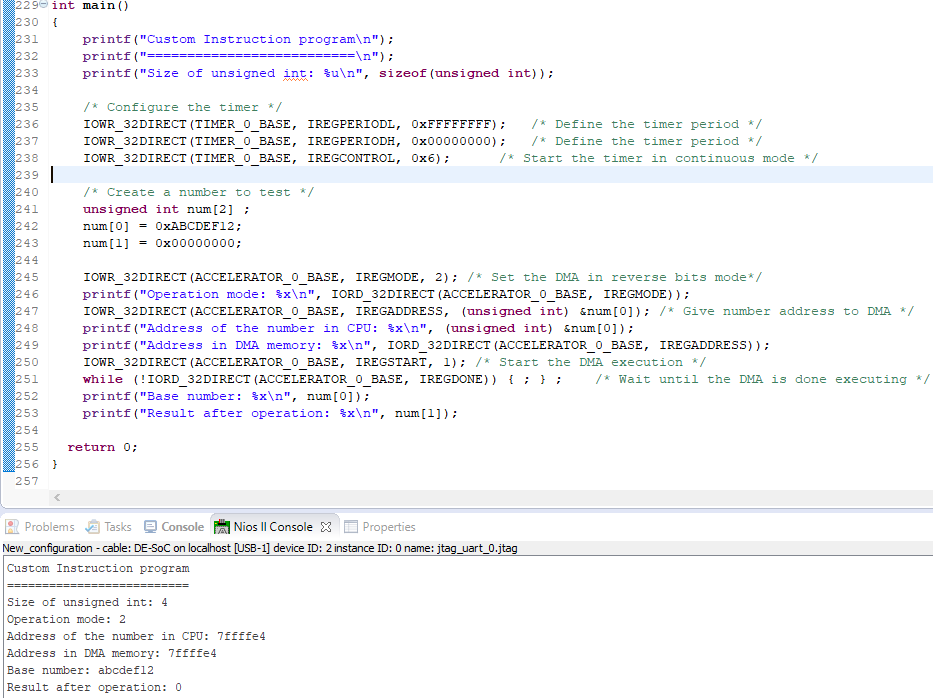

I designed a DMA accelerator to perform the bit/byte reversing/swapping operations as asked in the data. I simulated the design using Modelsim and it works smoothly.

My custom Avalon Master is able to perform a read access in the SDRAM. It can compute the new data from it to write it in the memory. All the signals are asserted at the output of my DMA. However, the data is never written in the SDRAM. When I read the data at the location it is supposed to write to, the DMA has not written anything in the memory.

Do you have an idea what could go wrong when the DMA writes in the memory? The byte_enable signal is set to "1111", I take into account wait_request as well.

Please find below a code snippet in C and the results in the Nios II console, along with a screenshot of the Signal Tap Analyzer I used to monitor the DMA signals.

Best regards,