Hello everybody

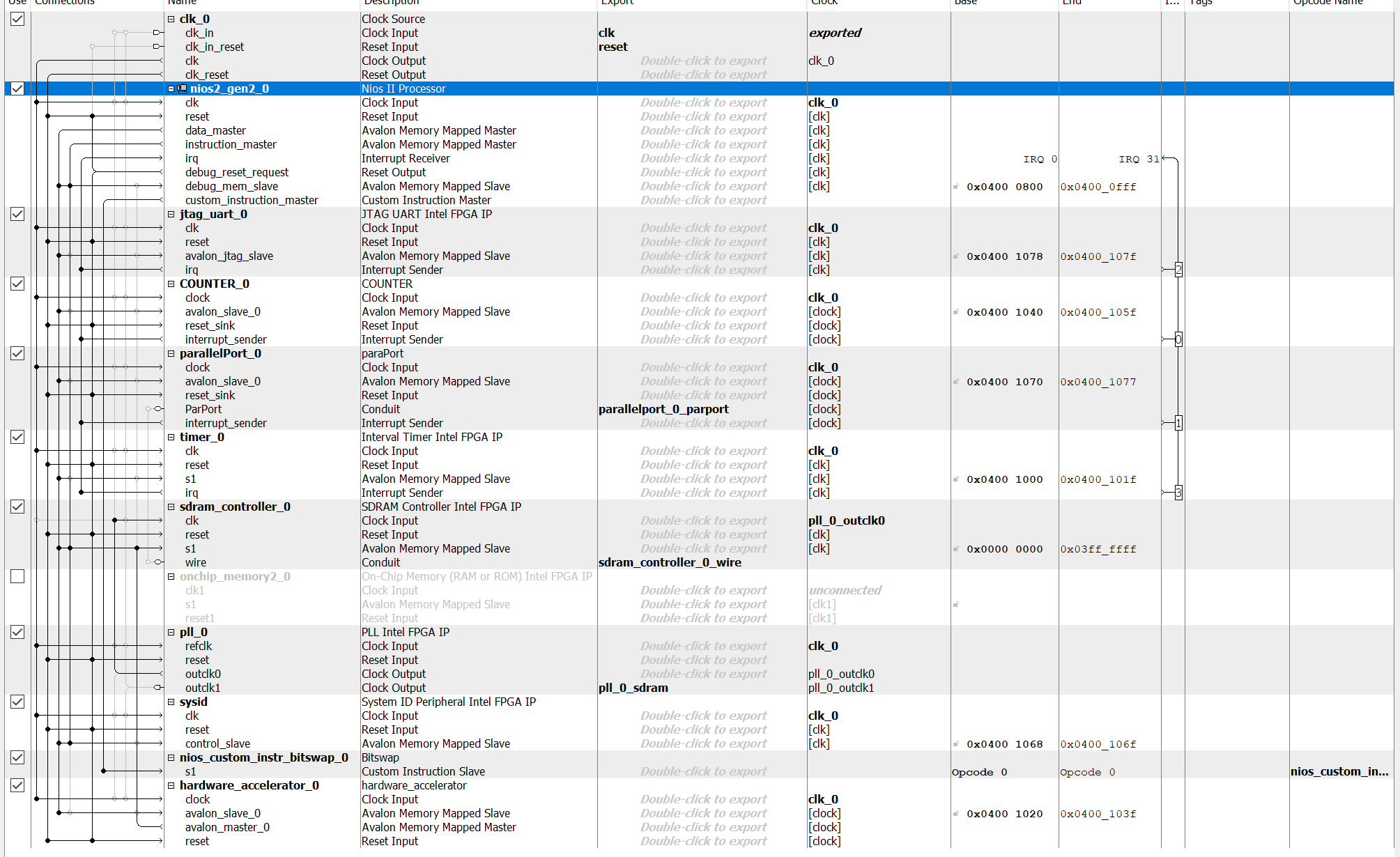

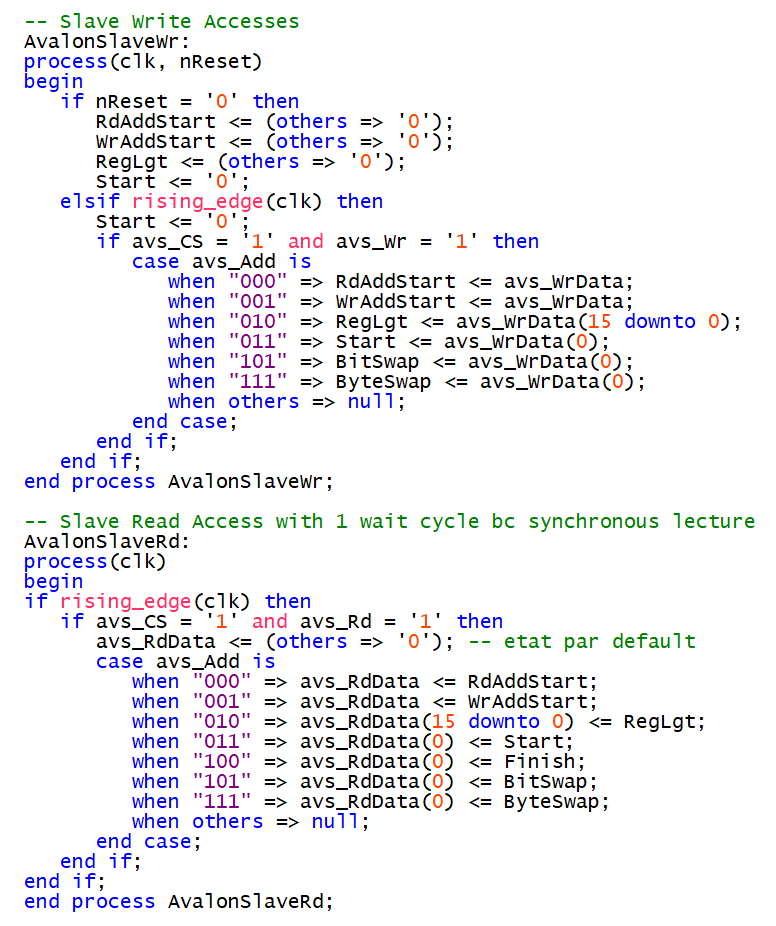

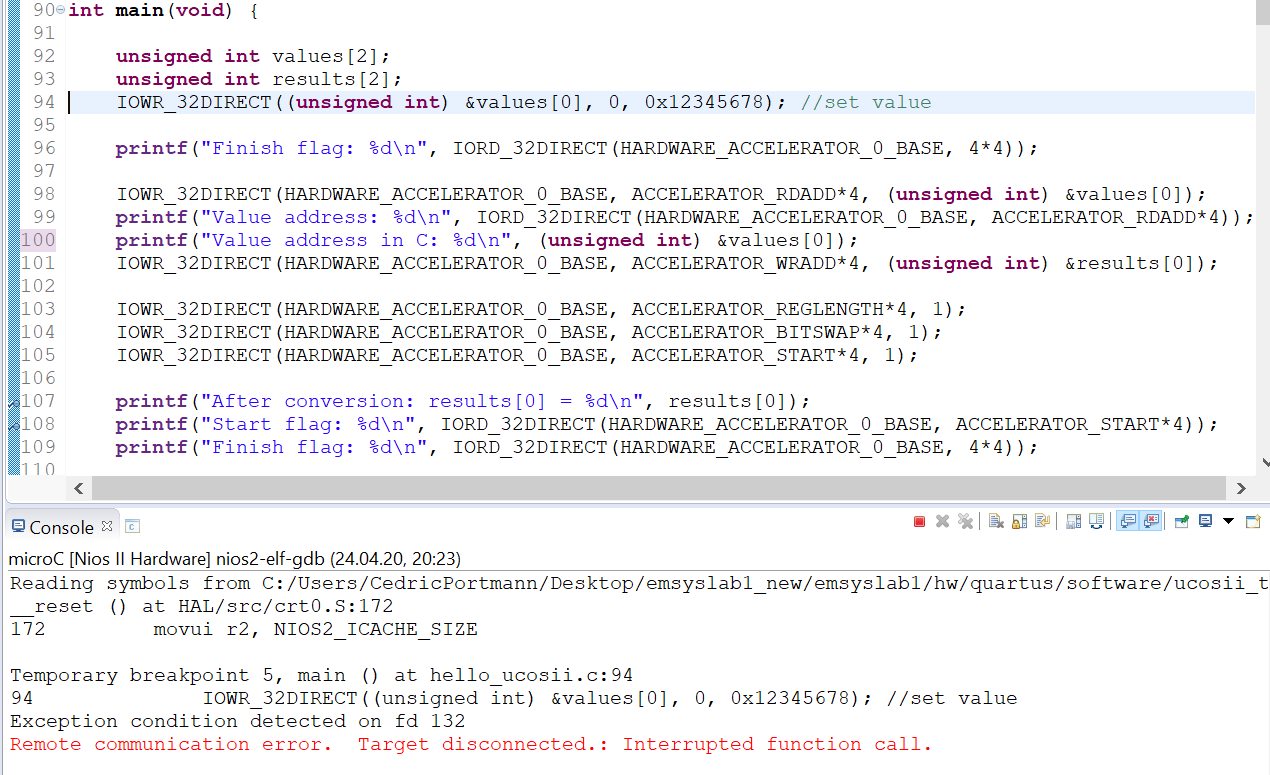

Concerning the accelerator DMA access: We are having trouble in C-code to print meaningful values. We tried multiple approaches with and without the IOWR_DIRECT macros. Either it doesnt change the values at all or the debugger gets stuck when we try to start the accelerator process, which leads us to beleiving that our Platform Designer configuration might be wrong. Are our accelerator signal connections correct? In addition I provide you the VHDL register configuration and a excerpt of the code in C (which doesnt work right now but might give you a better insight in what we are trying to do).

Thank you