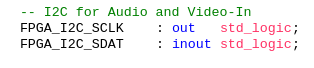

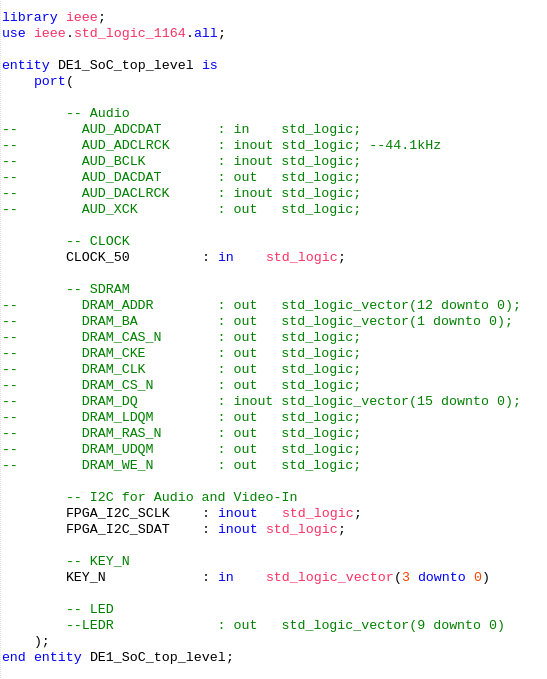

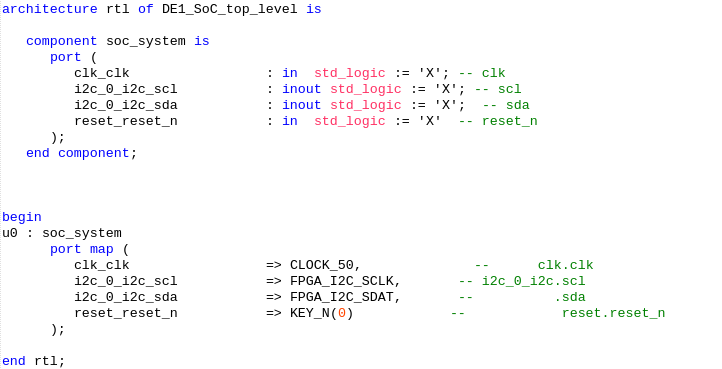

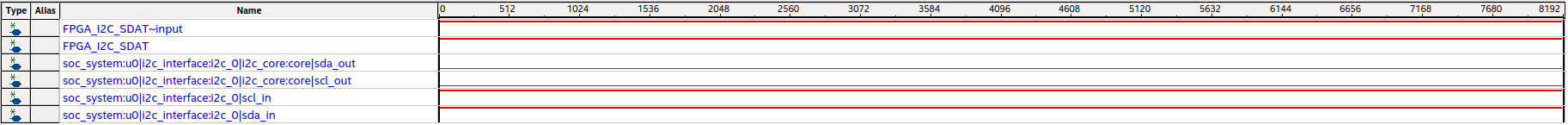

Hello, I am currently trying to setup a chip using the I2C IP component from qsys. It doesn't work (timeout error) but I don't really know how can I check what the problem is. I could spend my afternoon in debug mode and check what's the matter but I suspect my wiring to be wrong as I don't really understand why the IP component has an Opendrain enable and an input for each the clock and how to wire it as there are only two I2C lines for the audio components.

Any help would be greatly appreciated !

Thank you

Jon