Hello,

I'm having some trouble with the DMA accelerator an I can't figure out why.

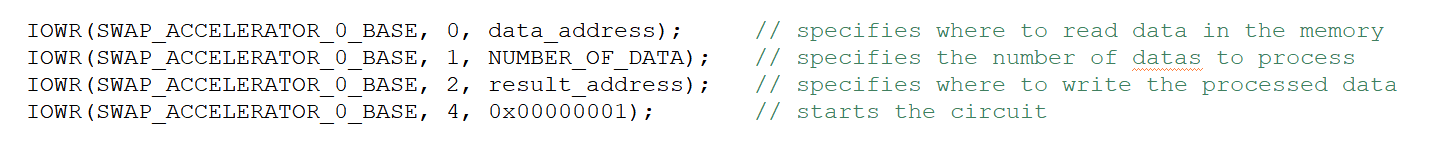

It works just fine but only when I set a debug breakpoint on any of the following instructions (which set up and start the circuit):

If I run the code normally, the circuit doesn't write anything in the memory. Even if I run the code in debug mode but without a breakpoint on these instructions, nothing happens.

I really have no idea why this is happening, maybe there is some issues with the arbitration of the bus?

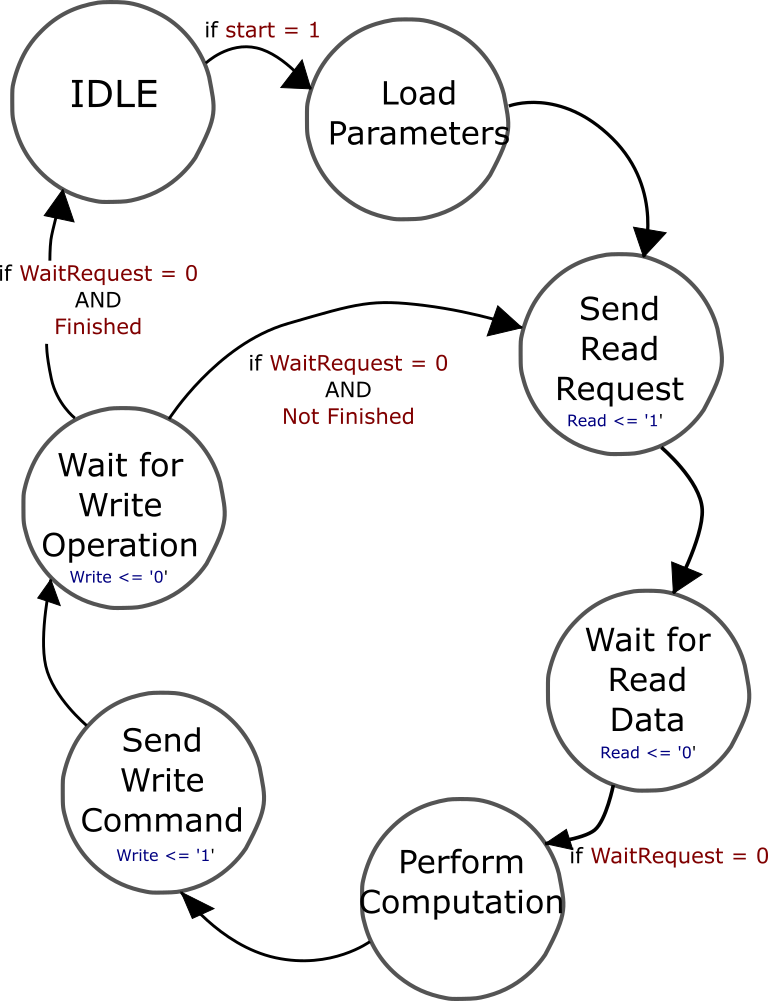

Or maybe I didn't design well my circuit... right now it does the following

- read 32 bits

- process them

- write the result in memory (at a different location)

- loop for every piece of data

Maybe I should have an internal buffer or a FIFO? Is it ok to read a piece of data at the time and write it immediately after?

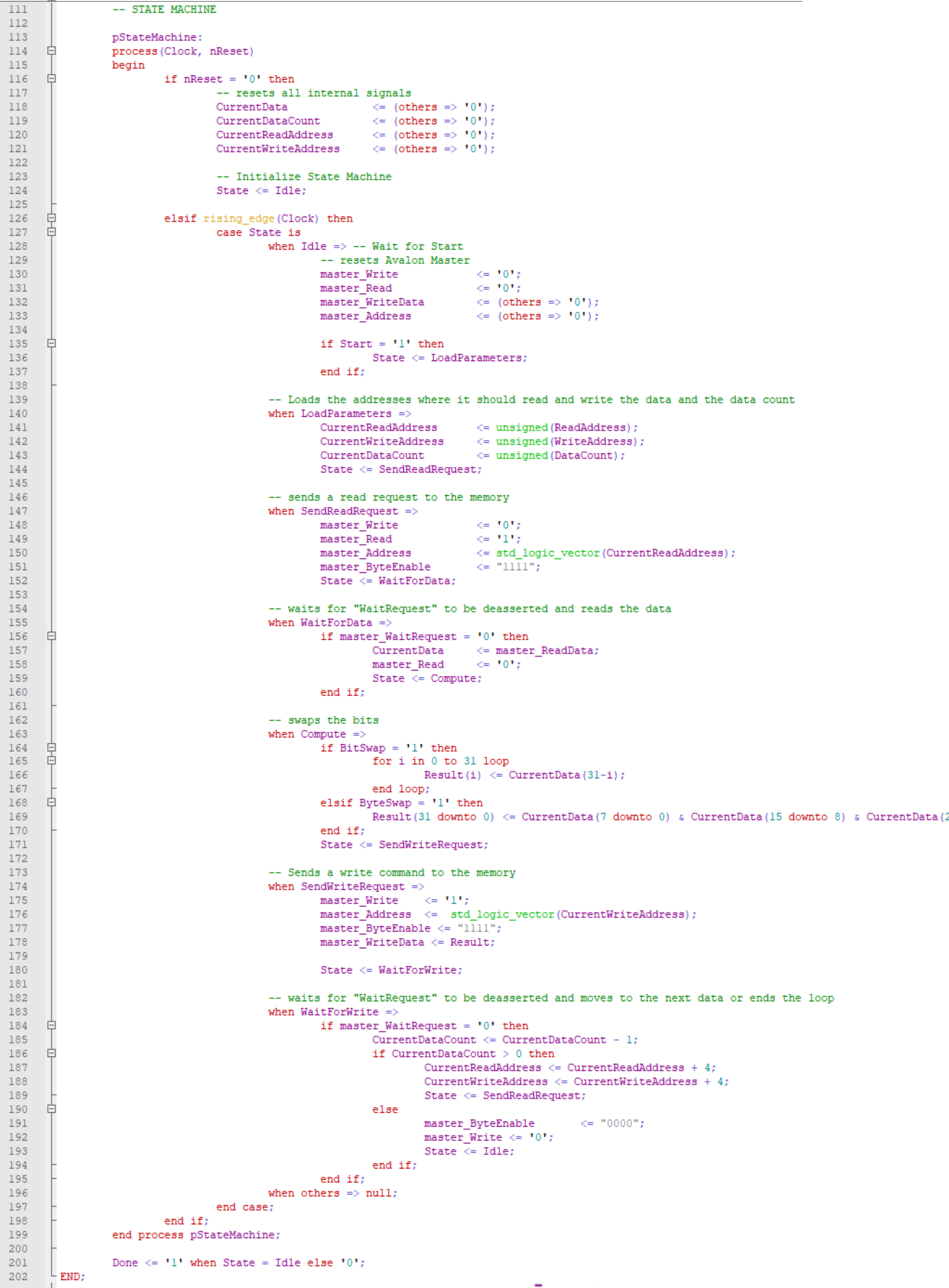

Here is my State Machine:

And here is my VHDL code:

Thanks a lot for your help!